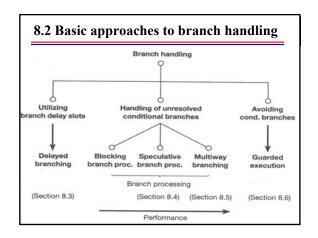

# 8 Processing of control transfer instructions

- 8.1 Introduction

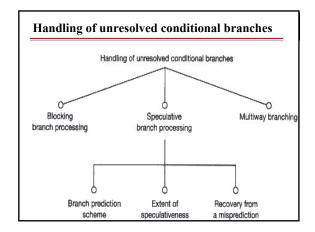

- 8.2 Basic approaches to branch handling

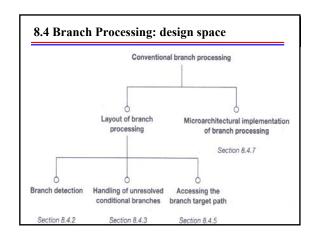

- · 8.3 Delayed branching

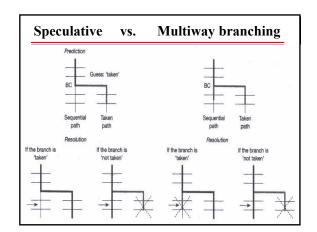

- · 8.4 Branch processing

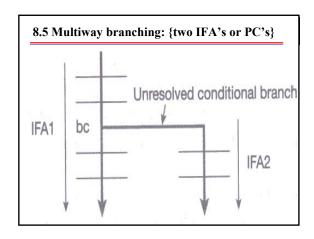

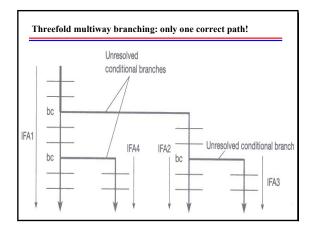

- · 8.5 Multiway branching

- · 8.6 Guarded execution

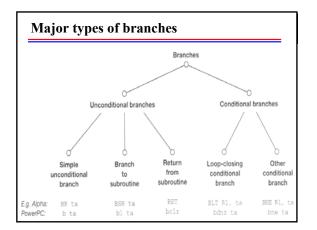

#### 8.1 Intro to Branch

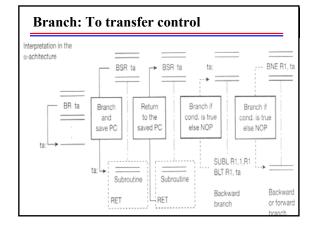

- Branches modify, conditionally or unconditionally, the value of the PC.

- · To transfer control

- To alter the sequence of instructions

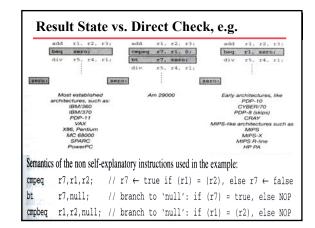

# Branch: e.g. Semantics of the non-self-explanatory instructions: BLT R1, ta // Branch if (R1) ≤ 0 SUBL R1,1,R1 // Decrement R1 by 1, BNE R1, ta // Branch to 'ta:' if (R1) ≠ 0 bl ta // Branch to 'ta:' and store next PC into the Link Register bclr // Branch to the address stored in the Link Register bdnz ta // Decrement Count Register, branch to 'ta:' if Count Register ≠ 0

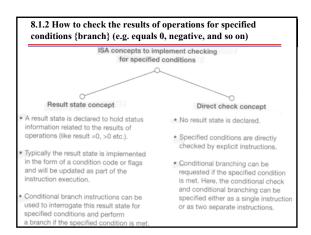

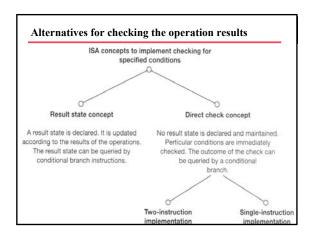

# Result state approach: Disadvantage

- The generation of the result state is not straightforward

- It requires an irregular structure and occupies additional chip area

- The result state is a sequential concept.

- It cannot be applied without modification in architectures which have multiple execution units.

# Retaining sequential consistency for condition checking (in VLIW or Superscalar)

- Use multiple sets of condition codes or flags

- It relies on programmer or compiler to use different sets condition codes or flags for different outcome generated by different EUs.

- Use Direct Check approach.

#### **Branch Statistics**

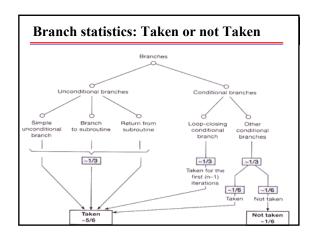

- 20% of general-purpose code are branch

- → on average, each fifth instruction is a branch

- 5-10% of scientific code are branch

- The Majority of branches are conditional (80%)

- 75-80% of all branches are taken

| Reference              | Frequency of taken branches | Frequency of untaken branches |

|------------------------|-----------------------------|-------------------------------|

| Lee and Smith, 1984    | 57-99%                      | 1–43 %                        |

| Edenfield et al., 1990 | 75 %                        | 25 %                          |

| Grohoski, 1990         | ~ 5/6                       | ~ 1/6                         |

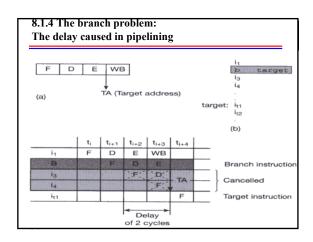

# More branch problems

- Conditional branch could cause an even longer penalty

- ÷ evaluation of the specified condition needs an extra cycle

- waiting for unresolved condition (the result is not yet ready)

- ≻ e.g. wait for the result of FDIV may take 10-50 cycles

- · Pipelines became more stages than 4

- + each branch would result in a yet larger number of wasted cycles (called bubbles)

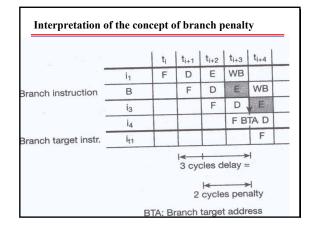

## 8.1.5 Performance measures of branch processing

- → Pt : branch penalties for taken

- → Pnt : branch penalties for not-taken

- → ft: frequencies of taken

- → fnt : frequencies for not-taken

- → P : effective penalty of branch processing

- P = ft \* Pt + fnt \* Pnt

- $\rightarrow$  e.g. 80386:: P = 0.75 \* 8 + 0.25 \* 2 = 6.5 cycles

- ightharpoonup e.g. i486:: P = 0.75 \* 2 + 0.25 \* 0 = 1.5 cycles

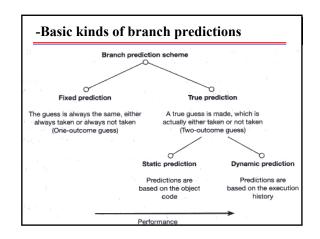

- · Branch prediction correctly or mispredicted

- P = fc \* Pc + fm \* Pm

- $\rightarrow$  e.g. Pentium:: P = 0.9 \* 0 + 0.1 \* 3.5 = 0.35 cycles

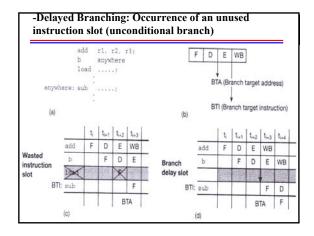

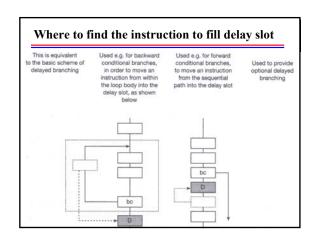

#### Basic scheme of delayed branching Principle of delayed branching t<sub>i+3</sub> b. b F D E WB D E add sub F D Branching to the target instruction (sub) is executed with one pipeline cycle of delay. This cycle is utilized to execute the instruction in the delay slot (add). Thus, delayed branching results in the following execution sequence: add b, sub

# **Delayed branching: Performance Gain**

- Ratio of the delay slots that can be filled with useful instructions::  $f_{\rm f}$

- → 60-70% of the delay slot can be fill with useful instruction

- fill only with: instruction that can be put in the delay slot but does not violate data dependency

- > fill only with: instruction that can be executed in single pipeline cycle

- Frequency of branches:: f<sub>b</sub>

- →20-30% for general-propose program

- →5-10% for scientific program

- 100 instructions have 100\* f<sub>b</sub> delay slots,

- 100\*f<sub>b</sub> \* f<sub>f</sub> can be utilized.

- Performance Gain =  $(100*f_b*f_f)/100 = f_b*f_f$

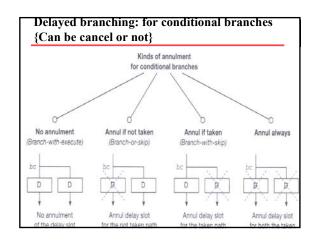

|                 | Annulment of an instruction in a delay slot |                    |                      |                 |                                  |  |

|-----------------|---------------------------------------------|--------------------|----------------------|-----------------|----------------------------------|--|

|                 | Branch-with-<br>execute                     | Branch-or-<br>skip | Branch-with-<br>skip | Annul<br>always | Multiplicity<br>of<br>delay slot |  |

| IBM 801 (1978)  | X                                           |                    |                      | Х               | 1                                |  |

| MIPS-X (1986)   | X                                           | X                  |                      |                 | 2                                |  |

| HP PA (1986)    | X                                           | $X^{i}$            | $X^2$                |                 | 1                                |  |

| SPARC (1987)    | X                                           | X                  |                      |                 | 1                                |  |

| MC 88100 (1988) | X                                           |                    |                      | X               | 1                                |  |

| i860 (1988)     |                                             | X                  |                      | X               | 1.                               |  |

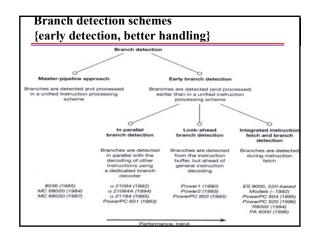

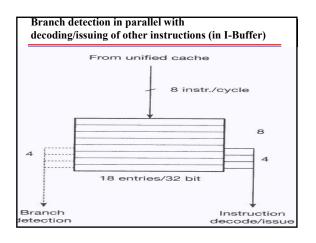

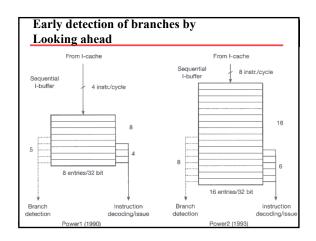

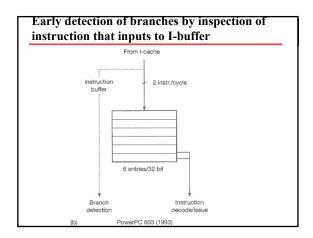

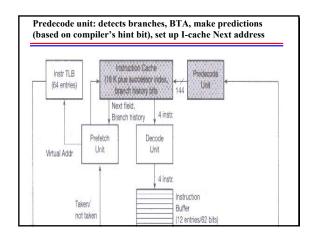

## Early branch detection: {for scalar Processor} Integrated instruction fetch and branch detection

- · Detect branch instruction during fetching

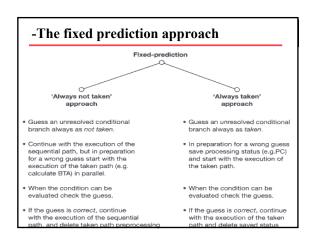

- · Guess taken or not taken

- · Fetch next sequential instruction or target instruction

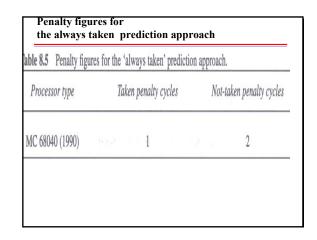

#### -Blocking branch processing • Simply stalled (stopped and waited) until the specified condition can be resolved Table 8.3 Branch penalties in blocking branch processing. Taken penalty Processor type Not-taken penalty cycles cycles MC 68020 (1984) 3 MC 68030 (1987) 5 3 80386 (1985) 8 2

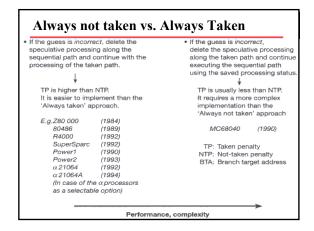

| Fable 8.4 Penalty figures for processors employing the 'always not taken' prediction<br>approach. |                      |                          |  |  |  |  |

|---------------------------------------------------------------------------------------------------|----------------------|--------------------------|--|--|--|--|

| Processor type                                                                                    | Taken penalty cycles | Not-taken penalty cycles |  |  |  |  |

| Z 80000 (1984p)                                                                                   | 3                    | 0                        |  |  |  |  |

| 80486 (1989p)                                                                                     | 2                    | 0                        |  |  |  |  |

| Power1 (1990)                                                                                     | 3                    | 0                        |  |  |  |  |

| R 4000 (1992p)                                                                                    | 3 (D)                | 0                        |  |  |  |  |

| SuperSparc (1992p)                                                                                | 1 (D)                | 0                        |  |  |  |  |

| Power2 (1993)                                                                                     | 1                    | 0                        |  |  |  |  |

| MicroSparc (1992)                                                                                 | 1 (D)                | 1 (D)                    |  |  |  |  |

|              | -                                 | in the MC 88110 (1993)    |            |

|--------------|-----------------------------------|---------------------------|------------|

|              | Instruction  Condition  specified | Bit 21 of the instr. code | Prediction |

|              | =0                                | 0                         | Not Taken  |

|              | ≠0                                | 1                         | Taken      |

| bend (Branch | >0                                | 1                         | Taken      |

| conditional) | <0                                | 0                         | Not Taken  |

|              | ≥0                                | 1                         | Taken      |

|              | ≤0                                | 0                         | Not Taken  |

| b            | b1 (Branch on bit so              | et)                       | Taken      |

| bb           | 0 (Branch on bit cle              | ear)                      | Not Taken  |

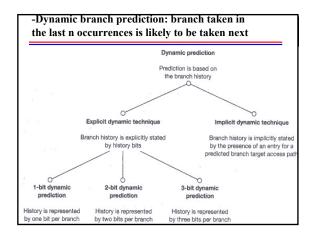

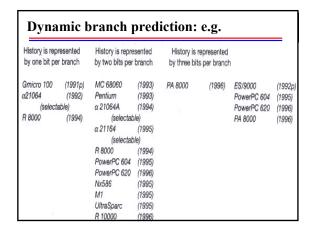

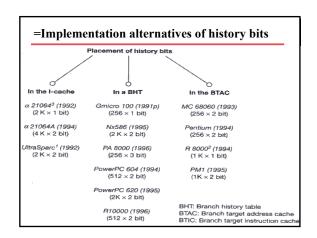

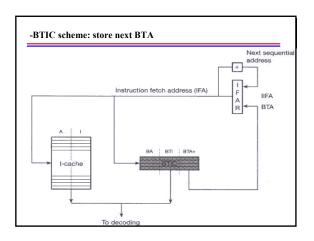

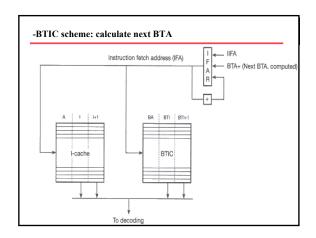

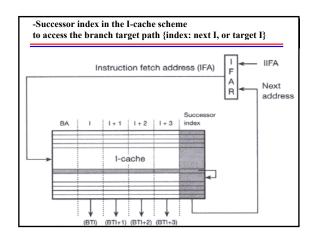

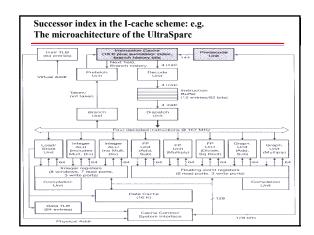

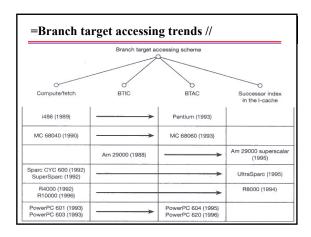

# Implicit dynamic technique

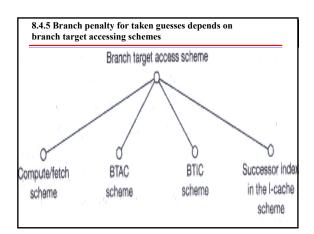

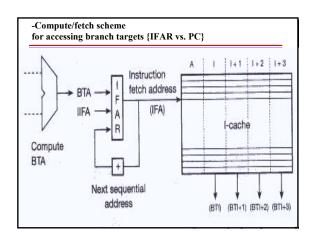

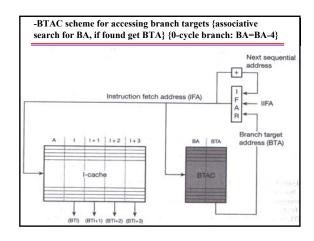

- Schemes for accessing the branch target path also used for branch prediction

- Branch Target Access Cache (BTAC)

- → holds the most recently used branch addresses

- Branch Target Instruction Cache (BTIC)

- → holds the most recently used target instructions

- BTAC or BTIC holds entries only for the taken branches

- · The existence of an entry means that

- the corresponding branch was taken at its last occurrence

- → so its next occurrence is also guessed as taken

| Table 8.7 Combining implicit and 2-bit prediction, as implemented in the PowerPC 604 (1995) and 620 (1996) processors. |                                 |                    |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------|--|--|--|--|

| BTAC                                                                                                                   | Outcome of the 2-bit prediction | Overall prediction |  |  |  |  |

| Hit                                                                                                                    | Don't care                      | Taken              |  |  |  |  |

| Miss                                                                                                                   | Taken                           | Taken              |  |  |  |  |

| Miss                                                                                                                   | Not taken                       | Not taken          |  |  |  |  |

|      |      | Overall prediction by combining implicit and 2-bit prediction, as implemented in the Pentium (1993) and MC 68060 (1993) processors. |                                 |                    |  |  |

|------|------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------|--|--|

| 71.0 | BTAC | 7                                                                                                                                   | Outcome of the 2-bit prediction | Overall prediction |  |  |

|      | Hit  |                                                                                                                                     | Taken                           | Taken              |  |  |

|      | Hit  |                                                                                                                                     | Not Taken                       | Not taken          |  |  |

|      | Miss |                                                                                                                                     | Don't care                      | Not taken          |  |  |

| able 8.9 The effect of branch accuracy or | branch accuracy on branch penalty (for $P_c = 0$ and $P_m = 4$ ). |  |  |

|-------------------------------------------|-------------------------------------------------------------------|--|--|

| Prediction accuracy (fc)                  | Branch penalty (P0) cycles                                        |  |  |

| 0.6                                       | 1.6                                                               |  |  |

| 0.8                                       | 0.8                                                               |  |  |

| 0.9                                       | 0.4                                                               |  |  |

| 0.95                                      | 0.2                                                               |  |  |

| Table 8.10 | Simulation results of prediction accuracy on the SPEC benchmark suite (Yeh and Patt, 1992). © 1992 ACM |                         |  |  |

|------------|--------------------------------------------------------------------------------------------------------|-------------------------|--|--|

|            | Prediction method                                                                                      | Prediction accuracy (%) |  |  |

|            | Fixed, always taken                                                                                    | 62.5                    |  |  |

| Sta        | tic, displacement based                                                                                | 68.5                    |  |  |

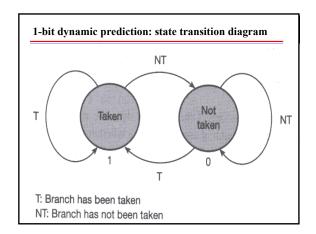

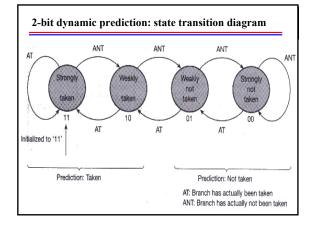

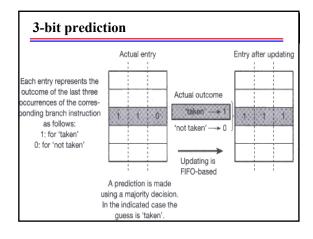

|            | Dynamic, 1-bit                                                                                         | 89                      |  |  |

|            | Dynamic, 2-bit                                                                                         | 93                      |  |  |

## 8.6 Guarded Execution

- · a means to eliminate branches

- · by conditional operate instructions

- → IF the condition associated with the instruction is met,

- → THEN perform the specified operation

- → ELSE do not perform the operation

- e.g. original

- $\rightarrow$  beg r1, label // if (r1) = 0 branch to label

- → move r2, r3 // move (r2) into r3

- →label: ...

- · e.g. guarded

- cmovne r1, r2, r3 // if (r1) != 0, move (r2) into r3

- <del>)</del> ..

- Convert control dependencies into data dependencies

# Eliminated branches by full and restricted guarding {full: all instruction guarded, restricted: ALU inst guarded}

| Program        | Damantan of I                      | Percentage of elin<br>Full guarding |         | ninated branches (%)<br>Restricted guarding |         |

|----------------|------------------------------------|-------------------------------------|---------|---------------------------------------------|---------|

| rnogram        | Percentage of loop<br>branches (%) | Cond.                               | Uncond. | Cond.                                       | Uncond. |

| -              | 10010                              |                                     |         |                                             |         |

| Compress       | 26.48                              | 24.86                               | 84.29   | 18.24                                       | 0.00    |

| Eqntott        | 29.07                              | 44.55                               | 54.98   | 40.04                                       | 1.02    |

| Espresso       | 38.08                              | 16.76                               | 29.03   | 10.17                                       | 1.17    |

| Gcc-cel        | 24.84                              | 31.92                               | 17.04   | 9.64                                        | 0.37    |

| Sc             | 24.63                              | 43.07                               | 17.74   | 9.83                                        | 0.18    |

| Sunbench       | 15.79                              | 35.65                               | 47.10   | 11.35                                       | 0.03    |

| Supermips      | 5.03                               | 50.69                               | 19.36   | 17.15                                       | 0.60    |

| Tektronix      | 16.83                              | 37.53                               | 41.60   | 17.08                                       | 7.48    |

| TeX            | 25.09                              | 12.80                               | 24.03   | 5.99                                        | 1.00    |

| Thissim        | 11.52                              | 62.31                               | 33.70   | 23.26                                       | 1.43    |

| Tycho          | 18.28                              | 15.64                               | 33.84   | 7.10                                        | 1.31    |

| Xlisp          | 27.03                              | 13.64                               | 14.33   | 13.87                                       | 14.14   |

| Yacc           | 38.64                              | 19.53                               | 38.95   | 8.18                                        | 1.71    |

| rithmetic Mean | 23.17                              | 31.15                               | 35.07   | 14.76                                       | 2.34    |

# **Guarded Execution: Disadvantages**

- guarding transforms instructions from both the taken and the not-taken paths into guard instruction

- increase number of instructions

- → by 33% for full guarding

- → by 8% for restricted guarding

- → {more instructions more time and space}

- guarding requires additional hardware resources if an increase in processing time is to be avoided

- → VLIW